|

伊利諾伊大學(xué)香檳分校和加州大學(xué)洛杉機分校的科研團隊正在研發(fā)一臺晶圓級計算機架構(gòu),其目標(biāo)旨在構(gòu)建多GPU芯片以芯片數(shù)據(jù)內(nèi)連連接(interconnect)的高效計算系統(tǒng),實現(xiàn)內(nèi)部數(shù)據(jù)互連的速率和能效,突破數(shù)據(jù)鏈路導(dǎo)致的性能瓶頸。

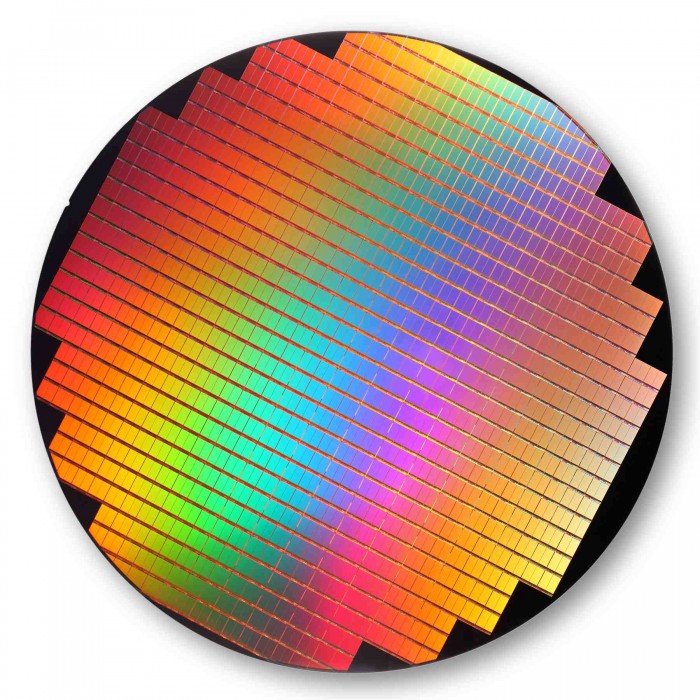

超級計算機中通常將一個任務(wù)應(yīng)用負(fù)載分散至單獨的印刷電路板的多GPU計算單元,這些GPU單元通過長途數(shù)據(jù)鏈路相互通信。數(shù)據(jù)鏈路成為了主要的瓶頸,因為它們的傳輸速度比芯片內(nèi)部數(shù)據(jù)互連要慢得多。 此外,“芯片和印刷電路板的存在機械性的不匹配”。意味著這些處理器必須包含在芯片封裝內(nèi),但這些封裝在輸入/輸出次數(shù)上是有限制的。 綜合起來數(shù)據(jù)鏈路就會產(chǎn)生顯著的性能瓶頸。如果是在理想情況下,多GPU模塊間數(shù)據(jù)通信可以和芯片內(nèi)部數(shù)據(jù)互連的速度/能效一樣高。 一種方法是把所有GPU都整合入同一塊硅晶圓的計算機,并且用芯片內(nèi)連連接它們。從規(guī)模生產(chǎn)上來看這種方法不現(xiàn)實,如果整合40個GPU入一個晶圓就足夠制造工藝災(zāi)難,很難保證如此規(guī)模項目中不存在某個制造瑕疵。 研究團隊采用了另一種方法:他們稱之為硅互連結(jié)構(gòu)(SiIF)的新技術(shù),使用通過質(zhì)量測試的標(biāo)準(zhǔn)GPU芯片,并用緊密集成的SiIF結(jié)構(gòu)更好地連接它們。從工程師的角度來看,其性能就是一個巨型的怪獸級GPU芯片,而非40個獨立GPU芯片并聯(lián)計算。 這種多GPU性能怪物的模擬計算速度提升19倍,并將綜合能耗和信號延遲的削減了140多倍。 伊利諾伊的計算機工程助理教授Rakesh Kumar和他的同事們已經(jīng)開始建造晶圓級原型,有望在2月IEEE國際高性能計算機體系結(jié)構(gòu)研討會上展示他們的研究成果。 |

- 關(guān)注天氣:

搜索